# **OPA671**

# Wide Bandwidth, Fast Settling *Difet®* OPERATIONAL AMPLIFIER

### FEATURES

- HIGH GAIN-BANDWIDTH: 35MHz

- LOW INPUT NOISE: 10nV/√Hz

- HIGH SLEW RATE: 100V/µs

- FAST SETTLING: 240ns to 0.01%

- FET INPUT:  $I_{B} = 50pA max$

- HIGH OUTPUT CURRENT: 50mA

- WIDE SUPPLY RANGE:  $V_s = \pm 4.5$  to  $\pm 18V$

## **APPLICATIONS**

- HIGH-SPEED DATA ACQUISITION

- OPTOELECTRONICS

- TRANSIMPEDANCE AMPLIFIER

- LINE DRIVER

- CCD BUFFER AMPLIFIER

### DESCRIPTION

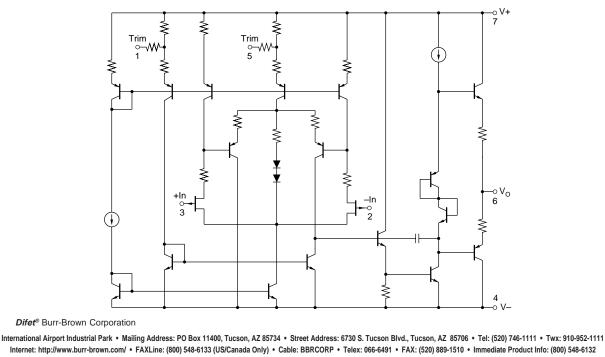

The OPA671 is a FET-input monolithic operational amplifier featuring wide bandwidth and fast settling time. Fabricated using Burr-Brown's **Difet**, complementary bipolar process, it provides an excellent combination of high speed, accuracy, and high output current.

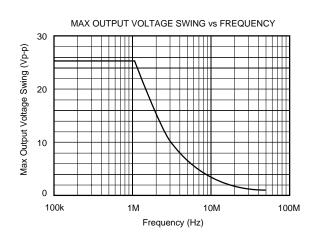

The OPA671 is versatile, operating from  $\pm 4.5V$  to  $\pm 18V$  power supplies. It can deliver  $\pm 10V$  signals into a 200 $\Omega$  load at slew rates of 100V/µs. OPA671's **Difet** input provides input bias current thousands of times lower than bipolar-input wideband op amps.

The OPA671 is internally compensated to be unity-gain stable, allowing use in the widest range of applications.

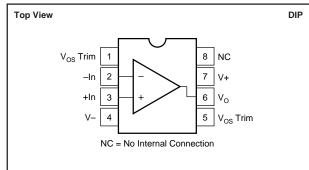

The OPA671 is available in an 8-pin plastic DIP, rated for the industrial temperature range.

© 1991 Burr-Brown Corporation

## **SPECIFICATIONS**

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 15V$ , unless otherwise noted.

| PARAMETER                                                                                                                                                                                                      | CONDITION                                                                                                                                                            | OPA671AP          |                                                  |                     | 1                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------|---------------------|---------------------------------------------------------|

|                                                                                                                                                                                                                |                                                                                                                                                                      | MIN               | TYP                                              | MAX                 | UNITS                                                   |

| OFFSET VOLTAGE<br>Input Offset Voltage<br>Average Drift<br>Power Supply Rejection                                                                                                                              | $V_{S} = \pm 4.5$ to $\pm 16.5V$                                                                                                                                     | 72                | ±0.5<br>±10<br>94                                | ±5                  | mV<br>μV/°C<br>dB                                       |

| INPUT BIAS CURRENT <sup>(1)</sup><br>Input Bias Current<br>Input Offset Current                                                                                                                                | V <sub>CM</sub> = 0V<br>V <sub>CM</sub> = 0V                                                                                                                         |                   | 5<br>2                                           | 50                  | pA<br>pA                                                |

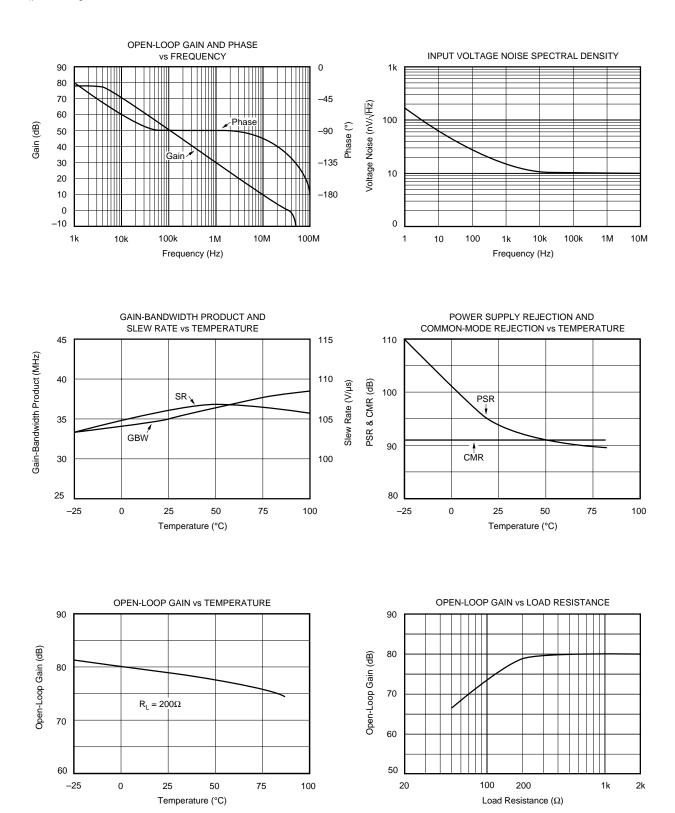

| NOISE<br>Input Voltage Noise<br>Noise Density, $f = 100Hz$<br>f = 1kHz<br>f = 10kHz<br>f = 100kHz<br>Voltage Noise, BW = 10Hz to 1MHz<br>Input Bias Current Noise<br>Current Noise Density, $f = 10Hz$ to 1MHz |                                                                                                                                                                      |                   | 24<br>15<br>12<br>10<br>60<br>2                  |                     | nV/\Hz<br>nV/\Hz<br>nV/\Hz<br>nV/\Hz<br>µVp-p<br>fA/\Hz |

| INPUT VOLTAGE RANGE<br>Common-Mode Input Range<br>Common-Mode Rejection                                                                                                                                        | V <sub>CM</sub> = ±10V                                                                                                                                               | ±12<br>74         | ±13<br>92                                        |                     | V<br>dB                                                 |

| INPUT IMPEDANCE<br>Differential<br>Common-Mode                                                                                                                                                                 |                                                                                                                                                                      |                   | 10 <sup>12</sup>    4.5<br>10 <sup>12</sup>    6 |                     | Ω    pF<br>Ω    pF                                      |

| OPEN-LOOP GAIN<br>Open-Loop Voltage Gain                                                                                                                                                                       | $V_O = \pm 10V, R_L = 1k\Omega$<br>$V_O = \pm 10V, R_L = 200\Omega$                                                                                                  | 74                | 80<br>78                                         |                     | dB<br>dB                                                |

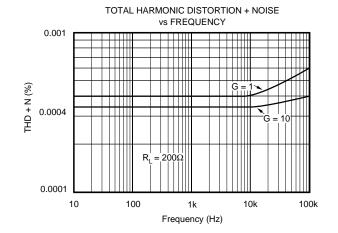

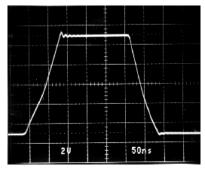

| FREQUENCY RESPONSE<br>Gain-Bandwidth Product<br>Slew Rate<br>Settling Time 0.01%<br>0.1%<br>1%<br>Total Harmonic Distortion                                                                                    | $G = -1, 10V \text{ Step}$ $G = 1, f = 100 \text{ KHz}$ $V_0 = 3V, R_L = 200\Omega$ |                   | 35<br>107<br>240<br>150<br>85<br>0.0006          |                     | MHz<br>V/μs<br>ns<br>ns<br>%                            |

| OUTPUT<br>Voltage Output<br>Current Output<br>Short Circuit Current<br>Output Resistance, Open-Loop                                                                                                            | $R_{L} = 200\Omega$ $V_{O} = \pm 10V$ DC                                                                                                                             | ±10.5             | ±11.5<br>50<br>-90/+105<br>20                    |                     | V<br>mA<br>mA                                           |

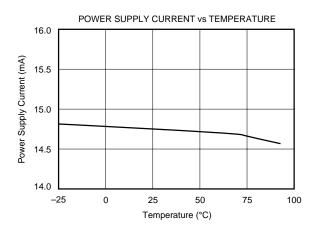

| POWER SUPPLY<br>Specified Operating Voltage<br>Operating Voltage Range<br>Quiescent Current                                                                                                                    | V <sub>S</sub> = ±15V                                                                                                                                                | ±4.5              | ±15<br>±14.8                                     | ±18<br>±17          | V<br>V<br>mA                                            |

| <b>TEMPERATURE RANGE</b><br>Specification<br>Operating<br>Storage<br>Thermal Resistance, θ <sub>JA</sub>                                                                                                       | Junction to Ambient                                                                                                                                                  | -25<br>-40<br>-40 | 100                                              | +85<br>+100<br>+125 | ې<br>ئ<br>گ                                             |

NOTE: (1) Tested without warm-up at  $T_J = T_A = 25^{\circ}C$ .

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **PIN CONFIGURATION**

### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage              | ±18V           |

|-----------------------------------|----------------|

| Input Voltage                     |                |

| Operating Temperature             |                |

| Storage Temperature               | 40°C to +125°C |

| Output Short-Circuit to Ground    | 15s            |

| Junction Temperature              | +150°C         |

| Lead Temperature (soldering, 10s) | +300°C         |

## ELECTROSTATIC DISCHARGE SENSITIVITY

An integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE           | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | TEMPERATURE<br>RANGE |

|----------|-------------------|---------------------------------------------|----------------------|

| OPA671AP | 8-Pin Plastic DIP | 006                                         | –25°C to +85°C       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

### **TYPICAL PERFORMANCE CURVES**

$T_{A} = +25^{\circ}C$ ,  $V_{S} = \pm 15V$  unless otherwise noted.

### TYPICAL PERFORMANCE CURVES (CONT)

$T_{_{\rm A}}$  = +25°C,  $V_{_{\rm S}}$  = ±15V unless otherwise noted.

INPUT BIAS CURRENT AND INPUT OFFSET CURRENT vs JUNCTION TEMPERATURE 1000 Input Bias And Offset Current (pA) 100 10 los 1 0 25 125 -25 0 50 75 100 Junction Temperature (°C)

# TYPICAL PERFORMANCE CURVES (CONT)

$T_{_A}$  = +25°C,  $V_{_S}$  =  $\pm 15V$  unless otherwise noted.

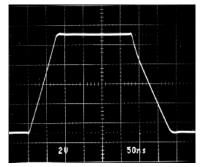

G = +1 LARGE SIGNAL RESPONSE

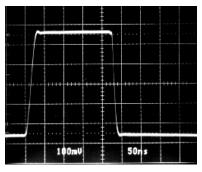

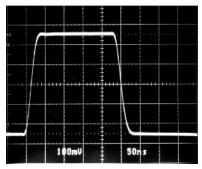

G = +1 SMALL SIGNAL RESPONSE

G = -1 LARGE SIGNAL RESPONSE

G = -1 SMALL SIGNAL RESPONSE

### **CIRCUIT LAYOUT**

With any high-speed, wide-bandwidth circuitry, careful circuit layout will ensure best performance. Make short, direct circuit interconnections and avoid stray wiring capacitance—especially at the inverting input pin. A component-side ground plane will help ensure low ground impedance. Do not place the ground plane under or near the inputs and feedback network.

The power supply connections should be bypassed with good high-frequency capacitors positioned close to the op amp pins. In most cases, both a  $1\mu$ F solid tantalum capacitor and a  $0.1\mu$ F ceramic capacitor are required on each supply. The OPA671 can deliver peak load currents up to 100mA. Even if steady-state load currents are lower, signal transients may demand large current transients from the power supplies. It is the power supply bypass capacitors which must supply these current transients. Larger bypass capacitors such as  $4.7\mu$ F solid tantalum capacitors may improve dynamic performance in some applications.

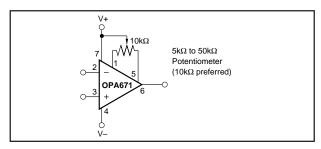

#### OFFSET ADJUSTMENT

Many applications require no external offset voltage adjustment. Figure 1 shows an optional circuit for trimming the offset voltage. Do not use this offset voltage adjustment to correct for offsets produced in other circuitry since this can introduce large offset voltage temperature drift.

FIGURE 1. Optional Offset Voltage Trim Circuit.

### CAPACITIVE LOADS

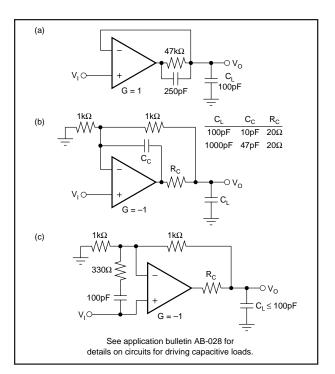

The OPA671 is internally compensated to be unity-gain stable with minimal capacitive load. The combination of low closedloop gain and capacitive load will decrease the phase margin and may lead to gain peaking or oscillations. Load capacitance reacts with the op amp's open-loop output resistance to form an additional pole in the feedback loop. With wideband op amps, load capacitance as low as 50pF can introduce enough phase shift to degrade dynamic performance. Figure 2 shows circuits which preserve phase margin with capacitive load. Request Application Bulletin AB-028 for details on various compensation circuits and analysis techniques.

#### POWER DISSIPATION

High output current can cause large internal power dissipation in the OPA671. Copper leadframe construction improves heat dissipation compared to conventional plastic packages. To achieve best heat dissipation, solder the device directly to the circuit board and use wide circuit board traces close to the device pins. Limit the ambient temperature, load and signal to

FIGURE 2. Compensation Circuits for Capacitive Loads.

assure that the maximum junction temperature is not exceeded. The OPA671 may be operated at reduced power supply voltage to minimize power dissipation.

#### **OUTPUT CURRENT LIMIT**

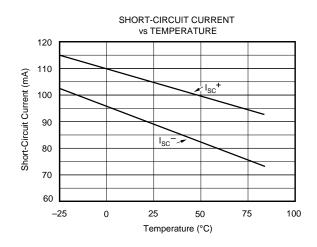

Output current is limited by internal circuitry to approximately 90mA at 25°C. The short-circuit limit current decreases with increasing junction temperature as shown in the typical curves. The current limit will protect the device from inadvertent short-circuits to ground. The internal power dissipation under this condition, however, is quite high so short-circuits should be avoided.

#### INPUT BIAS CURRENT

The OPA671 is fabricated with Burr-Brown's dielectrically isolated **Difet** process, giving it extremely low input bias current. As with other FET-input amplifiers, input bias current approximately doubles with every 10°C increase in junction temperature. Input bias current can be minimized by soldering the device to the circuit board to provided best heat dissipation. Reduced power supply voltage will also minimize input bias current by reducing internal power dissipation.

#### **DEMONSTRATION BOARD**

The OPA671 may be evaluated using a high frequency PC board developed for the OPA65x op amp family. This board may be ordered from your local Burr-Brown distribution as part # DEM-OPA65xP. It comes partially assembled but does not include the amplifier. Since this board was intended for  $\pm$ 5V amplifier, verify that any electrolytic capacitors loaded on the board can support the higher supply voltages possible with the OPA671.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated